This is a Plain English Papers summary of a research paper called FPGA Divide-and-Conquer Placement using Deep Reinforcement Learning. If you like these kinds of analysis, you should subscribe to the AImodels.fyi newsletter or follow me on Twitter.

Overview

- The paper presents a deep reinforcement learning approach for FPGA placement, a critical step in the electronic design automation (EDA) process.

- It introduces a divide-and-conquer strategy to tackle the complex FPGA placement problem, breaking it down into smaller, more manageable sub-problems.

- The proposed method leverages deep neural networks to learn efficient placement policies, aiming to outperform traditional EDA tools.

Plain English Explanation

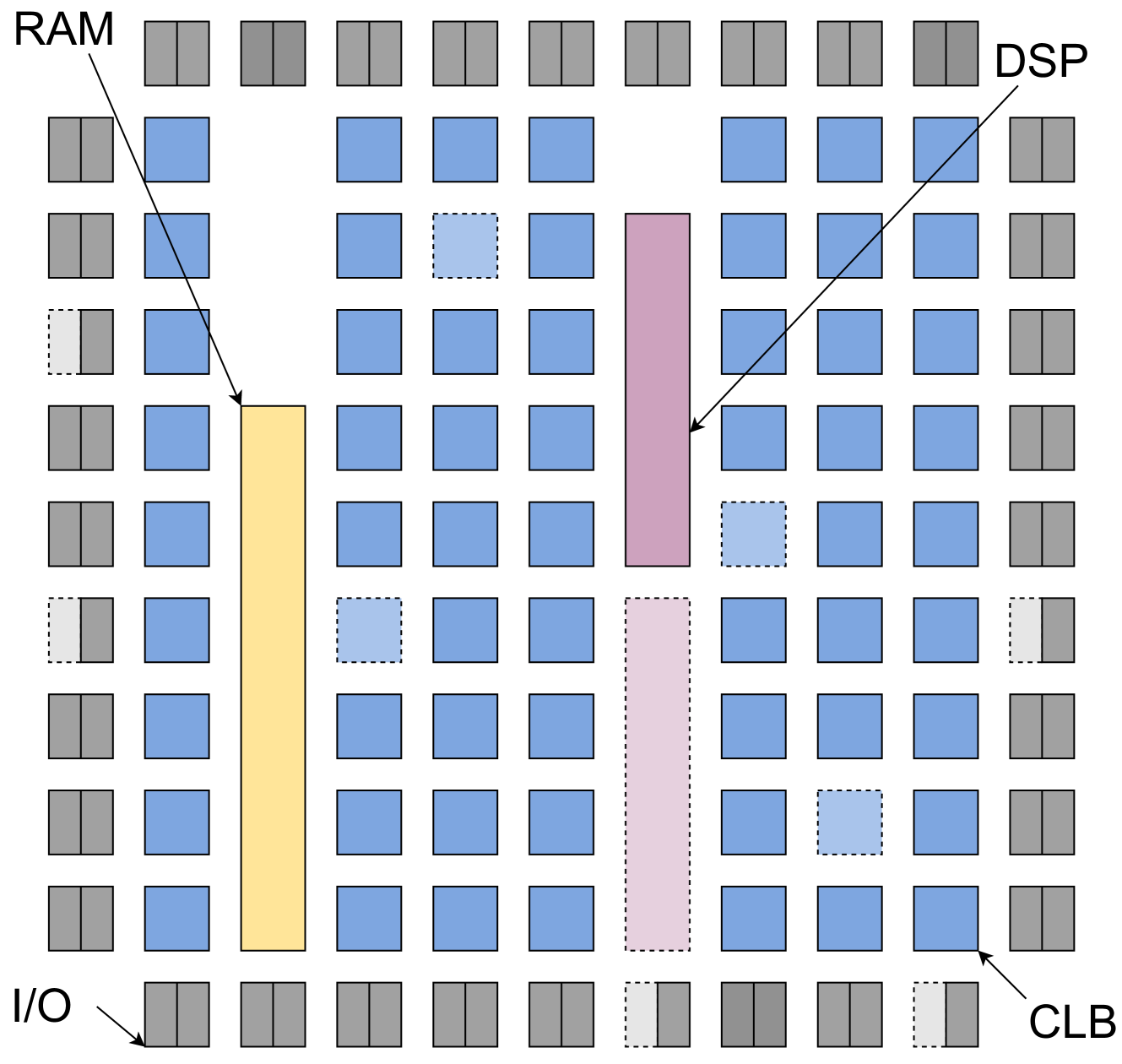

Field Programmable Gate Arrays (FPGAs) are a type of semiconductor device that can be programmed to perform specific tasks. Placing the various components of an FPGA design in the optimal locations is a crucial step in the FPGA placement process, as it significantly impacts the performance and efficiency of the final circuit.

The researchers in this paper recognized the complexity of the FPGA placement problem and developed a novel approach using deep reinforcement learning. Reinforcement learning is a type of machine learning where an agent learns to make decisions by interacting with an environment and receiving rewards or penalties for its actions.

The key idea is to break down the FPGA placement problem into smaller, more manageable sub-problems, using a "divide-and-conquer" strategy. This allows the deep neural network to learn placement policies for each sub-problem, rather than trying to solve the entire problem at once. The researchers train the neural network by having it explore different placement options and learn from the feedback it receives, much like a human learning a new skill through trial and error.

This divide-and-conquer approach, combined with the power of deep learning, aims to outperform traditional EDA tools for FPGA placement, leading to more efficient and high-performing FPGA designs.

Technical Explanation

The paper presents a deep reinforcement learning-based approach for FPGA placement, a critical step in the electronic design automation (EDA) process. The authors tackle the complex FPGA placement problem using a divide-and-conquer strategy, breaking it down into smaller, more manageable sub-problems.

The core of the proposed method is a deep neural network that learns efficient placement policies for each sub-problem. The neural network takes the current state of the FPGA placement problem as input and outputs a placement decision for the next set of components. The network is trained using deep reinforcement learning, where it explores different placement options and learns from the feedback it receives, aiming to maximize a reward signal that reflects the quality of the placement.

The divide-and-conquer strategy is implemented by recursively partitioning the FPGA area into smaller regions, and then assigning components to these regions using the trained neural network. This approach allows the system to tackle large-scale FPGA placement problems by breaking them down into smaller, more manageable sub-problems.

The researchers evaluate their method on a range of FPGA benchmark circuits and compare its performance to traditional EDA tools. The results demonstrate that the proposed deep reinforcement learning-based approach can outperform existing techniques, leading to more efficient and high-performing FPGA designs.

Critical Analysis

The paper presents a promising approach to FPGA placement using deep reinforcement learning, but there are a few potential limitations and areas for further research that could be explored.

One key concern is the computational complexity of the divide-and-conquer approach, which may still be challenging for very large FPGA designs. The authors mention that the method can handle large-scale problems, but the scalability of the technique could be further investigated, especially as FPGA designs continue to grow in size and complexity.

Additionally, the paper focuses on optimizing a single objective (e.g., wirelength or congestion), but in practice, FPGA placement often involves balancing multiple, sometimes conflicting objectives. Extending the approach to handle multi-objective optimization could be an interesting area for future research, as seen in constrained object placement using reinforcement learning.

Another potential limitation is the reliance on a single deep neural network for the entire placement process. Exploring alternative architectures, such as model-based deep reinforcement learning or advancing forest fire prevention with deep reinforcement learning, could lead to further improvements in placement quality and efficiency.

Overall, the paper presents a novel and promising approach to FPGA placement using deep reinforcement learning. While the method shows strong performance, the authors have identified several areas for potential improvement, which could be valuable avenues for future research in this field.

Conclusion

This paper introduces a deep reinforcement learning-based approach for FPGA placement, a critical step in the electronic design automation (EDA) process. The key innovation is the use of a divide-and-conquer strategy, where the complex FPGA placement problem is broken down into smaller, more manageable sub-problems.

The proposed method leverages deep neural networks to learn efficient placement policies for each sub-problem, aiming to outperform traditional EDA tools. The results demonstrate the effectiveness of this approach, which could lead to more efficient and high-performing FPGA designs.

While the paper presents a promising solution, there are opportunities for further research to address potential limitations, such as scalability, multi-objective optimization, and alternative neural network architectures. Continued advancements in this area could have significant implications for the field of electronic design automation and the development of more powerful and energy-efficient FPGA-based systems.

If you enjoyed this summary, consider subscribing to the AImodels.fyi newsletter or following me on Twitter for more AI and machine learning content.